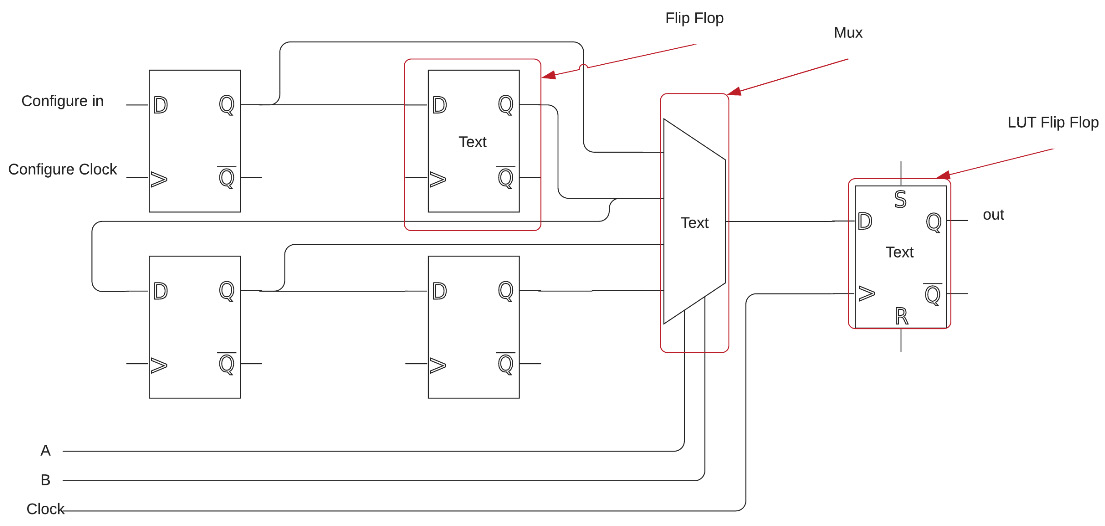

A single 6-input LUT can store 64 bits.ĭistributed ram is read asynchronously, but written to synchronously (requires a clock). Distributed ram is, as its name suggests, distributed throughout the FPGA. LUTs are usually used to create the logic of your design, but can also support memory in some FPGAs. Distributed RAMĭistributed ram is built with LUTs. The Lattice iCE40 UP5K has 5,280 flip-flops, while the Xilinx Spartan 7S25 has 29,200. Logic cnt = 0 // 16 flip-flopsįlip-flops are great for saving state, but they’re not ideal for all but the smallest memories: their numbers are limited, they’re spread throughout the FPGA (making routing larger memories hard), and they don’t support multiple ports. When you create a simple counter you’re using flip-flops: Flip-Flopsįlip-flops are the state keepers of FPGAs. The same memory capacity could also be organised as 256K x 16, which means it has 262,144 (256 x 1024) locations, each of which holds 16 bits. For example, a 4 Mb SRAM could be described as 512K x 8, which means it has 524,288 (512 x 1024) locations, each of which holds 8 bits. Memory is described by its organisation or depth x width. ProTip: In SystemVerilog you can use $clog2 to calculate the address width from the depth.

0 kommentar(er)

0 kommentar(er)